瑞萨RA系列FSP库开发实战指南之QSPI通讯协议简介

第23章

QSPI——读写外部FLASH

我们在上一章中已经学习过关于SPI协议的通讯实验,在本章我们将继续学习关于SPI协议的另一个分支——QSPI。

23.1

QSPI协议简介

QSPI是Queued SPI的简写,是Motorola公司推出的SPI接口的扩展,比SPI应用更加广泛。在SPI协议的基础上,Motorola公司对其功能进行了增强,增加了队列传输机制,推出了队列串行外围接口协议(即QSPI协议)。QSPI是一种专用的通信接口,连接单、双或四(条数据线)SPIFlash存储介质。

该接口可以在以下三种模式下工作:

1. 间接模式:使用QSPI寄存器执行全部操作;

2. 状态轮询模式:周期性读取外部Flash状态寄存器,而且标志位置1时会产生中断(如擦除或烧写完成,会产生中断);

3. 内存映射模式:外部Flash映射到微控制器地址空间,从而系统将其视作内部存储器。

采用双闪存模式时,将同时访问两个Quad-SPI Flash,吞吐量和容量均可提高二倍。

QSPI是Quad SPI的简写,表示6线SPI,是Motorola公司推出的SPI接口的扩展,比SPI应用更加广泛。

在SPI协议的基础上,Motorola公司对其功能进行了增强,增加了队列传输机制,推出了队列串行外围接口协议(即QSPI协议)。

使用该接口,用户可以一次性传输包含多达16个8位或16位数据的传输队列。一旦传输启动,直到传输结束,都不需要CPU干预,极大的提高了传输效率。该协议在ColdFire系列MCU得到广泛应用。

23.1.1

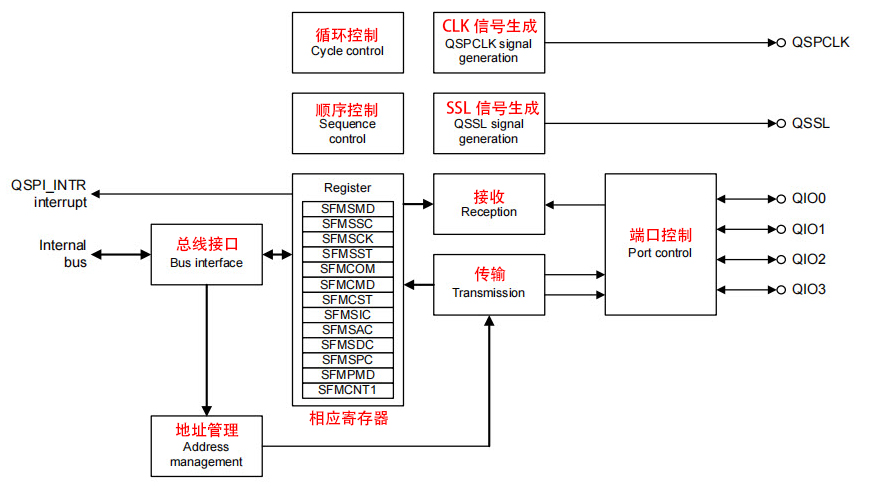

QSPI功能框图

QSPI是一个内存控制器,用于连接具有SPI兼容接口的串行ROM(非易失性存储器,如串行闪存、串行EEPROM或串行FeRAM)。

注

QSPI常用的寄存器有通信端口寄存器(SFMCOM)以及通信方式控制寄存器(SFMCMD)

23.1.2

QSPI引脚的定义

我们的开发板采用的是双闪存禁止的模式连接单片QSPI Flash。QSPI使用6个信号连接Flash,分别是四个数据线QIO0~QIO3,一个时钟输出CLK,一个片选输出(低电平有效)QSSL,它们的作用介绍如下:

(1)QSSL:片选输出(低电平有效),适用于FLASH1。如果QSPI始终在双闪存模式下工作,则其也可用于FLASH2从设备选择信号线。QSPI通讯以QSSL线置低电平为开始信号,以QSSL线被拉高作为结束信号。

(2)CLK:时钟输出,适用于两个存储器,用于通讯数据同步。它由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,两个设备之间通讯时,通讯速率受限于低速设备。

(3)QIO0:在双线/四线模式中为双向IO,单线模式中为串行输出,适用于FLASH1。

(4)QIO1:在双线/四线模式中为双向IO,单线模式中为串行输入,适用于FLASH1。

(5)QIO2:在四线模式中为双向IO,适用于FLASH1。

(6)QIO3:在四线模式中为双向IO,适用于FLASH1。

23.1.3

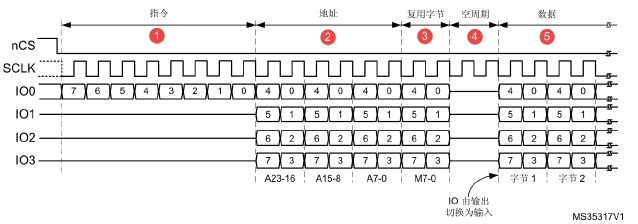

QSPI命令序列

QUADSPI通过命令与Flash通信每条命令包括指令、地址、交替字节、空指令和数据这五个阶段,任一阶段均可跳过,但至少要包含指令、地址、交替字节或数据阶段之一。nCS在每条指令开始前下降,在每条指令完成后再次上升。先看看QSPI四线模式下的读命令时序,见下图。

23.1.4

QSPI内存映射模式

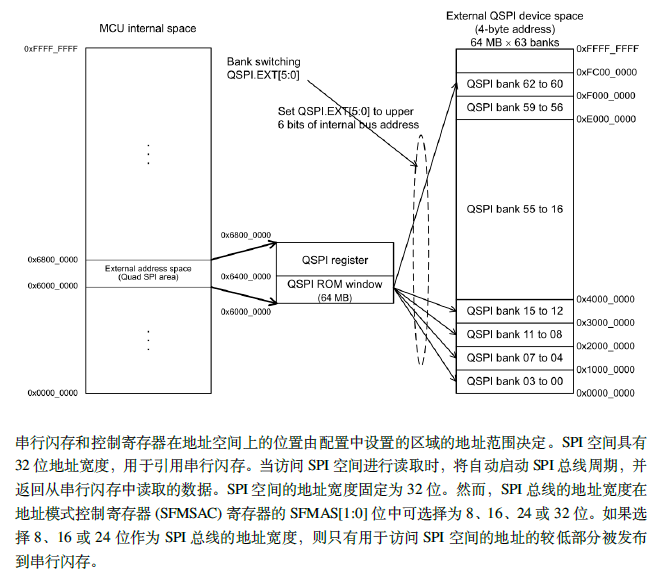

外部QSPI设备空间映射到内部空间如图所示:

外部总线的空间

串行闪存和控制寄存器在地址空间上的位置由配置中设置的区域的地址范围决定。SPI空间具有32位地址宽度,用于引用串行闪存。当访问SPI空间进行读取时,将自动启动SPI总线周期,并返回从串行闪存中读取的数据。SPI空间的地址宽度固定为32位。

然而,SPI总线的地址宽度在地址模式控制寄存器(SFMSAC)寄存器的SFMAS[1:0]位中可选择为8、16、24或32位。如果选择8、16或24位作为SPI总线的地址宽度,则只有用于访问SPI空间的地址的较低部分被发布到串行闪存。